5.2 Diseño del Simulador

El simulador implementado adopta la arquitectura de Von Neumann, reconocida por su simplicidad conceptual y operativa. En este modelo, los datos y las instrucciones comparten una única memoria, lo que permite tratar las instrucciones como datos. Esta característica facilita técnicas como la ejecución dinámica y la optimización del rendimiento (Stallings 2021).

VonSim2 sirvió como referencia por su enfoque educativo e interfaz intuitiva. Sobre esta base se desarrolló VonSim83, adaptado para operar con registros y memoria de 8 bits y diseñado para el aprendizaje progresivo (Facundo Quiroga 2020).

La arquitectura detallada de VonSim, con su amplio repertorio de instrucciones y componentes, ofrece una visión integral del sistema. Sin embargo, dicha riqueza funcional puede abrumar a estudiantes en etapas iniciales. Por esta razón, VonSim8 introduce una simplificación estrategica, con el objetivo de reducir la carga cognitiva en etapas iniciales, facilitando así una apropiación gradual de los conceptos fundamentales. A partir de esta base, se introdujeron diversas modificaciones en los componentes, instrucciones y funcionalidades del simulador, priorizando aquellos aspectos conceptuales que se abordan en el programa de la asignatura.

VonSim (Facundo Quiroga 2020) es una herramienta diseñada específicamente para la enseñanza y el aprendizaje de la arquitectura y organización de computadoras. Sus principales características la posicionan como una solución educativa integral:

Características técnicas y pedagógicas de VonSim:

Entorno integrado de desarrollo y simulación: Proporciona un entorno completo que incluye editor de código ensamblador con resaltado de sintaxis y un simulador para la ejecución de programas, facilitando el proceso de aprendizaje práctico (Facundo Quiroga 2020).

Fundamento en arquitectura real: Se basa en el procesador Intel 8088, proporcionando una referencia histórica y técnicamente relevante para el estudio de la evolución de las arquitecturas de computadoras (Intel Corporation 1979).

Componentes esenciales para el estudio: Incluye cuatro registros multipropósito de 16 bits, memoria principal de 32 kB, bus de direcciones de 16 bits y bus de datos de 8 bits, abarcando los elementos fundamentales para la comprensión de la arquitectura von Neumann (Stallings 2021).

Gestión completa de interrupciones: Implementa tanto interrupciones por software (entrada/salida de datos) como interrupciones por hardware mediante un controlador de interrupciones programable (PIC), cubriendo aspectos fundamentales de la operación del sistema (John L. Hennessy and Patterson 2017a).

Simulación de periféricos: Incorpora dispositivos como reloj, llaves, LEDs e impresora Centronics, inspirados en los especificados por la familia iAPX 88 de Intel, permitiendo simular interacciones complejas con el sistema.

Enfoque pedagógico mediante simplificaciones estratégicas: No pretende ser un emulador fiel del 8088, sino una herramienta educativa que implementa simplificaciones deliberadas (repertorio de instrucciones reducido y codificación simplificada) para facilitar la comprensión en contextos educativos (Patt and Patel 2019).

Desarrollo académico especializado: Creado por Facundo Quiroga, Manuel Bustos Berrondo y Juan Martín Seery, con colaboración de Andoni Zubimendi y César Estrebou, específicamente para las cátedras de Organización de Computadoras y Arquitectura de Computadoras de la Facultad de Informática de la Universidad Nacional de La Plata, garantizando su alineación con objetivos curriculares específicos.

Fundamento en experiencia previa: Se apoya en el simulador MSX88, desarrollado en 1988 por Rubén de Diego Martínez para la Universidad Politécnica de Madrid, aprovechando décadas de experiencia acumulada en simuladores educativos.

Accesibilidad y sostenibilidad: Distribuido bajo licencia GNU Affero General Public License v3.0 con código fuente disponible en GitHub, y documentación bajo licencia CC BY-SA 4.0, facilitando su estudio, modificación y mejora continua (Open Source Initiative 2024).

En síntesis, VonSim constituye una herramienta robusta y accesible que simplifica y facilita el aprendizaje de conceptos complejos de arquitectura de computadoras mediante simulación práctica y una interfaz pedagógicamente orientada.

Las modificaciones principales de VonSim8, alineadas con objetivos pedagógicos, incluyen:

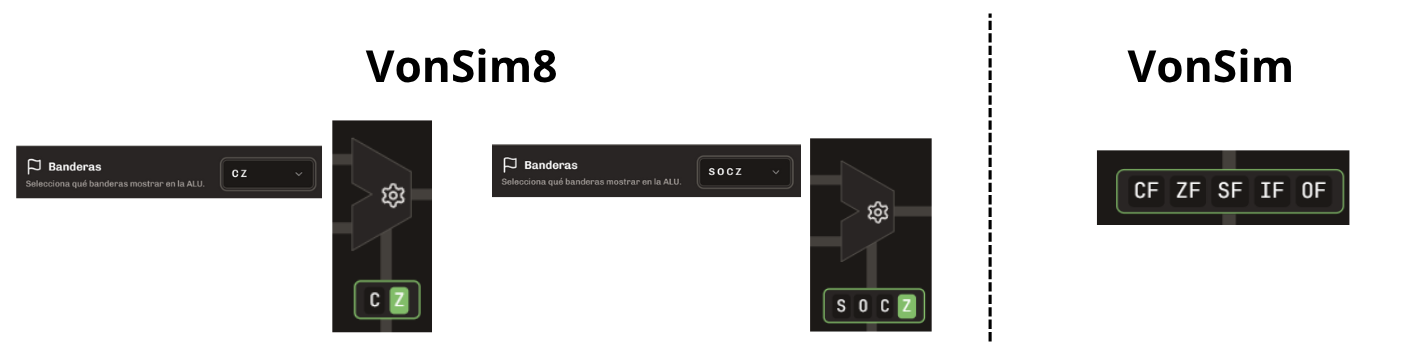

El registro de estado contiene los siguientes flags o banderas: Z = cero (Zero) C = acarreo (Carry) S = signo (Sign) O = desbordamiento (Overflow) I = interrupción (Interrupt)

5.2.1 Flags

El registro FLAGS es un registro de 8 bits que contiene las flags mostradas en la siguiente tabla. Este registro no es directamente accesible por el usuario, pero puede ser modificado por las operaciones de la ALU y pueden realizarse saltos condicionales en base a sus valores.

| Bit # | Abreviatura | Descripción |

|---|---|---|

| 0 | Z |

Flag de cero |

| 1 | C |

Flag de acarreo |

| 2 | O |

Flag de overflow |

| 3 | S |

Flag de signo |

| 4 | I |

Flag de interrupción |

El resto de bits del registro de estado están reservados.

Del registro de estado del simulador original se ocultaron las banderas O y S ya que en los primeros ejercicios de ensamblador no se requiere su uso ya que se trabaja solamente con números enteros positivos, posteriormente las mismas se pueden habilitar en el menu configuración del simulador.

Figura 5.7: Registro de estado

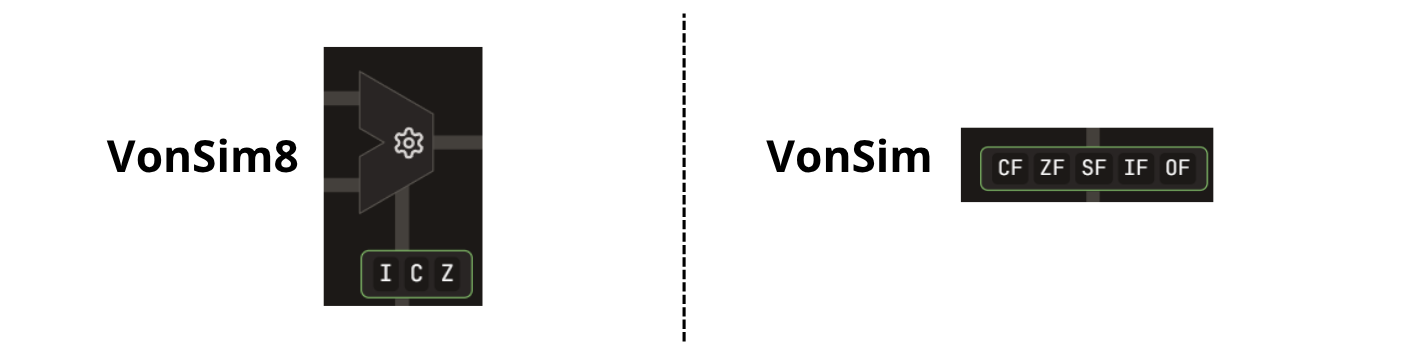

El flag de interrupcion I solo se muestra cuando el programa lo requiere, por ejemplo, al ejecutar una instrucción de interrupción como INT o IRET. Esto permite a los estudiantes observar cómo se activa y desactiva este flag en función de las operaciones realizadas.

Figura 5.8: Registro de estado I

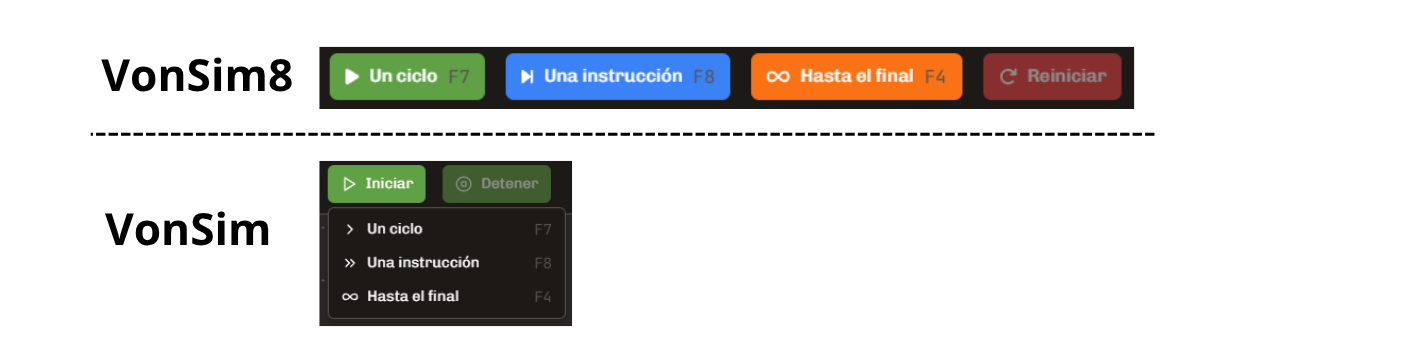

Figura 5.9: Controles del simulador

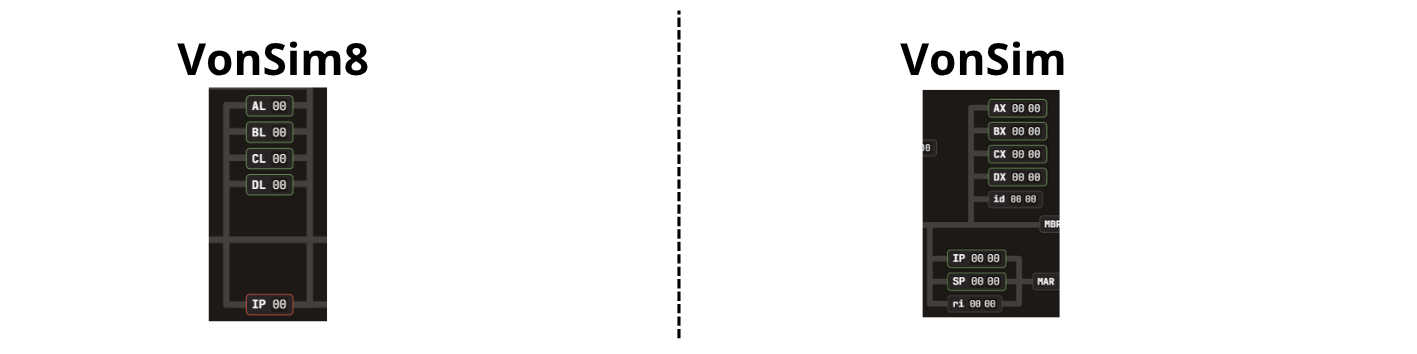

Se eliminaron los registros de 16 bits y se redujo el tamaño de los registros a 8 bits, lo que simplifica la representación y manipulación de datos. Esta decisión se fundamenta en la necesidad de reducir la complejidad del modelo para facilitar la comprensión de los conceptos fundamentales de la arquitectura de computadoras. Tambien se unifico el criterio del diseño de los registro, ahora todos los registros tienen una entrada y una salida independiente, lo que permite una visualización más clara de cómo se transfieren los datos entre los registros y la ALU (Unidad Aritmético Lógica). Esta modificación es esencial para comprender el flujo de datos en el ciclo de instrucción y la interacción entre los componentes del procesador. Tambien se ocultaron los registros registro SP y (ri e id) que se habilitan automaticamente al ejecutar una instrucción que requiera su uso.

Figura 5.10: Registro de 8 bits

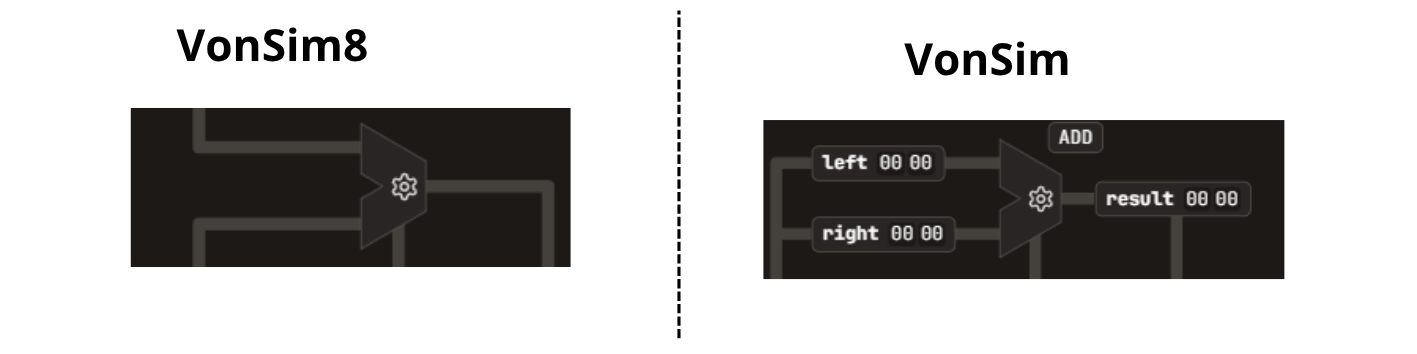

Se elimino el uso de los registros temporales de la ALU (left y rigth).

Por una cuestion de diseño del simulador algunos registros tienen la entrada y salida de manera horizontal y otros vertical, pero su funcionamiento es el mismo.

Figura 5.11: Eliminación registro temporales left y rigth

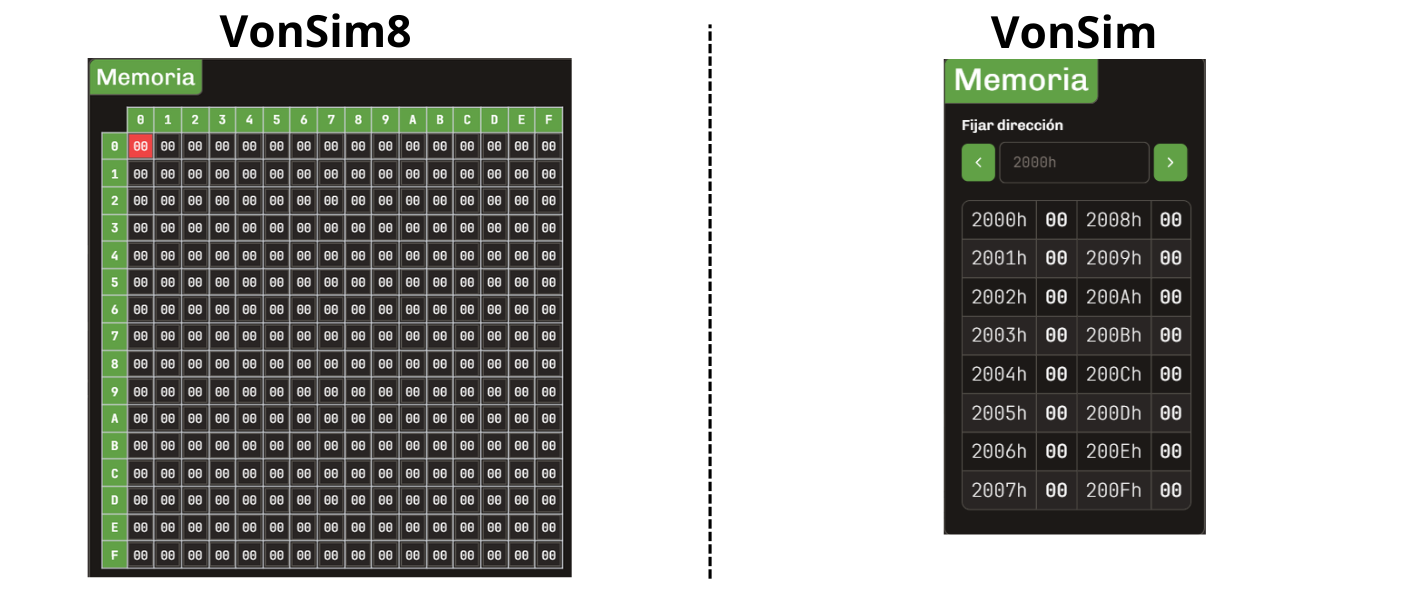

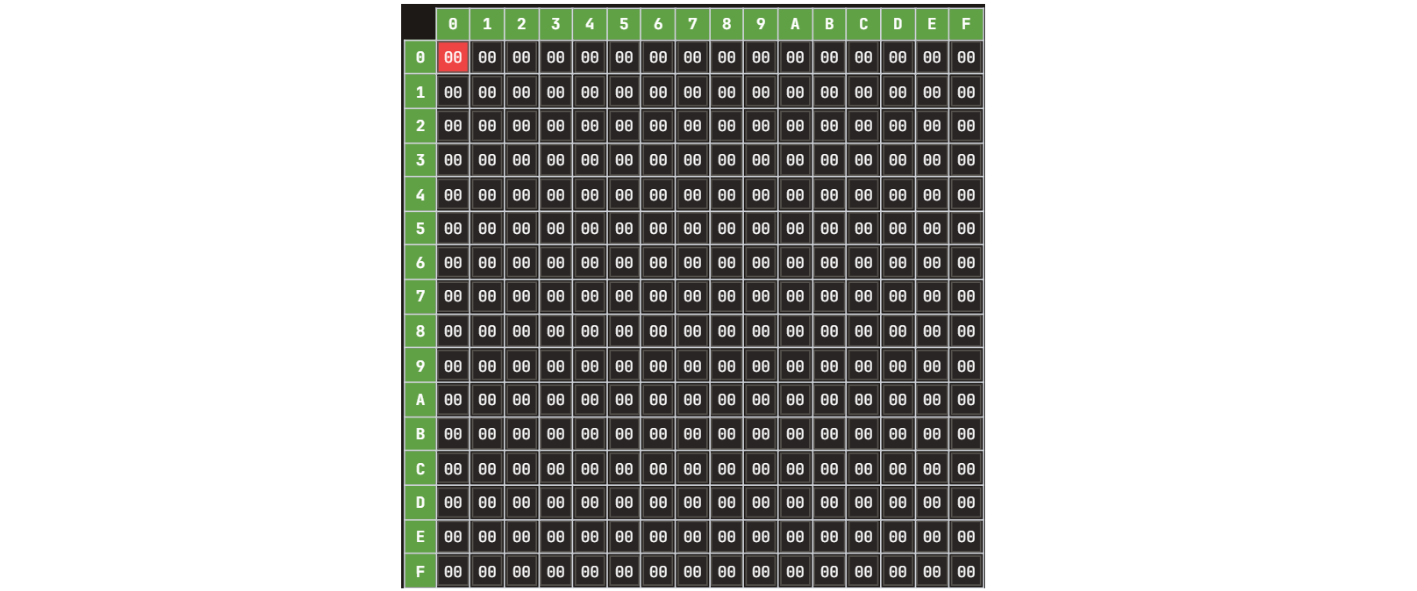

La memoria principal se modela como una matriz de 16×16 expresada en hexadecimal, lo que permite almacenar hasta 256 bytes de datos.

Figura 5.12: Memoria principal

Resaldo de la direccion de memoria apuntada por el registro IP.

Figura 5.13: Resaltado registro IP

Cuando el progrma tiene instrucciones INT o de manejo de pila se resalta en memoria el el vector de interrucciones, 8 posiciones de memoria desde 0x00 a 0x07 y la dirección apuntada por el registro SP:

Figura 5.14: Resaltado vector de interrupciones y registro SP

Visor de instrucciones y datos del programa en memoria, pudiendo ver la instruccion y su tamaño en bytes que ocupa en memoria, ademas la etiqueta asociada a los datos.

Figura 5.15: Resaltado vector de interrupciones y registro SP

En el VonSim cuando se escribe un programa en el editor del simulador es obligatorio que la sección de codigo inicie con la directiva org 0x2000h, porque el simulador comienza a ejecutar la primer instrucción del programa a partir de la dirección de memoria 0x2000h, esto se indica al comienzo del programa mediante la directiva org 0x2000h y los datos del programa generalmente se cargan a partir de la dirección de memoria 0x1000h mediante la directiva org 0x1000h.

En VonSim8 no es obligatorio la directiva org para indicar la dirección de inicio del programa sino opcional, por default si el programa no tiene la directiva org la primer instruccion del programa comienza a cargarse en la dirección 0x00h, y en caso que el programa tenga instrucciones de interrupcion INT el programa se cargará a partir de la direccion 0x08h para dejar espacio al vector de interrupciones.

VonSim8 tambien permite cargar el programa de manera similar como VonSim pero en utilizar la directiva org 0x2000h utiliza org 0x20h y el simulador comienza a ejecutar la instruccion que se encuentra en la dirección 0x20h de la memoria vez de cargar en la posicion ya que el simulador asigna automáticamente la dirección 0x00 al primer byte del programa. Esto simplifica la escritura de programas y evita errores comunes relacionados con la asignación manual de direcciones.

Pero si el programa requiere una dirección de inicio específica, se puede utilizar la directiva org para establecerla. Por ejemplo, org 0x20h indicaría que el programa debe comenzar en la dirección 0x20 de la memoria. Por compatibilidad con el simulador VonSim, se mantiene la directiva org para aquellos usuarios que deseen especificar una dirección de inicio diferente a la predeterminada. Sino se especifica la directiva org en el programa el simulador comienza a ejecutar el programa desde la dirección 0x00h, en caso de que el programa tenga instrucciones de interrupción INT, el simulador asigna automáticamente la dirección 0x08h al primer byte del programa, dejando espacio para el vector de interrupciones.

El simulador tiene predefinido el vector de interrupción en ciertas posiciones de reservadas de memoria, dentro de dicho vector encontraremos las rutinas del sistema predefinidas para interactuar con el teclado y monitor.

En el caso de las interrupciones por software, esta es dada por el operando de la instrucción INT número. Una vez interrumpido, el procesador ejecutará la rutina de interrupción asociada a ese número de interrupción. La dirección de comienzo de esta rutina estará almacenada en el vector de interrupciones. Este vector ocupa las celdas 00h hasta 07h de la memoria principal, y cada elemento del vector tiene 1 byte de largo – el primer elemento se encuentra en 0h, el segundo en 1h, el tercero en 2h, y así. Cada elemento corresponde con la dirección de inicio de la rutina de interrupción.

Específicamente, el procesador:

- obtiene el número de la interrupción (0-7),

- apila el registro

FLAGS, - inhabilita las interrupciones

IF=0, - apila el registro

IP, - obtiene la dirección de la rutina de interrupción del vector de interrupciones,

- modifica el

IPpara que apunte a la dirección de la rutina de interrupción.

El simulador implementas las interrupciones por software mediante la instrucción INT <n>. Estos números son:

INT 0: termina la ejecución del programa, equivalente a la instrucciónHLT;INT 6: lee un carácter del teclado;INT 7: escribe una cadena de caracteres en pantalla.

5.2.2 Requisitos funcionales del simulador VonSim8

Simplificación del repertorio instruccional para una introducción gradual;

Reducción a registros y memoria de 8 bits, coherente con la escala de enseñanza;

Interfaz gráfica esquemática que muestra el flujo de ejecución;

Funciones interactivas para observar explícitamente el ciclo de instrucción y la interacción de componentes.

Las modificaciones implementadas se alinean con los contenidos curriculares de la asignatura y están fundamentadas en los principios del aprendizaje activo (Bonwell and Eison 1991).

5.2.3 Estructura del VonSim8

Esta sección describe la estructura del simulador VonSims8, el diseño de los registros fue concebido para facilitar la comprensión de los modos de direccionamiento y del ciclo de instrucción, ambos considerados fundamentos clave en el estudio de la Arquitectura de Computadoras (Stallings 2021). Se describe en la siguiente tabla ?? los componentes principales del simulador, junto con sus características y funcionalidades específicas. Esta tabla proporciona una visión general de la arquitectura del simulador, destacando los elementos clave que componen su estructura y su propósito pedagógico.:

Dentro de los registros específicos que no pueden ser accedidos por el usuario, se encuentra el registro SP (stack pointer) para el funcionamiento de la pila, el registro FLAGS (flags register), el IP (instruction pointer) que almacena la dirección de la próxima instrucción a ejecutar, el IR (instruction register) que almacena el byte de la instrucción que se está analizando/decodificando en un instante dado. También hay 2 registros dedicados a la transferencia de información entre la CPU y la memoria principal: el MAR (memory address register) encargado de almacenar direcciones de memoria, y el MBR (memory buffer register) que almacena el byte que se quiere propagar o se ha recibido por el bus de datos.

Además, dos registros específicos que sirven de intermediarios para realizar ejecutar instrucciones, como pueden ser el ri para almacenar una dirección temporal, el id para almacenar un dato temporal.

Bibliografía

VonSim: https://vonsim.github.io/↩︎