5.3 Ciclo de la instrucción: Etapas de captación y ejecución

En este apartado se detalla el proceso llevado a cabo por la Unidad de Control (UC) para ejecutar cada instrucción, destacando los aspectos clave:

- Secuencia de pasos.

- Registros involucrados en cada etapa del proceso.

- Uso de los buses de datos, direcciones y control.

- Señales de control generadas.

El ciclo de la instrucción se define como la secuencia de microoperaciones necesarias para ejecutar una instrucción en el sistema. Estas microoperaciones se expresan mediante un lenguaje de transferencia entre registros, representado de la forma:

destino \(\leftarrow\) origen

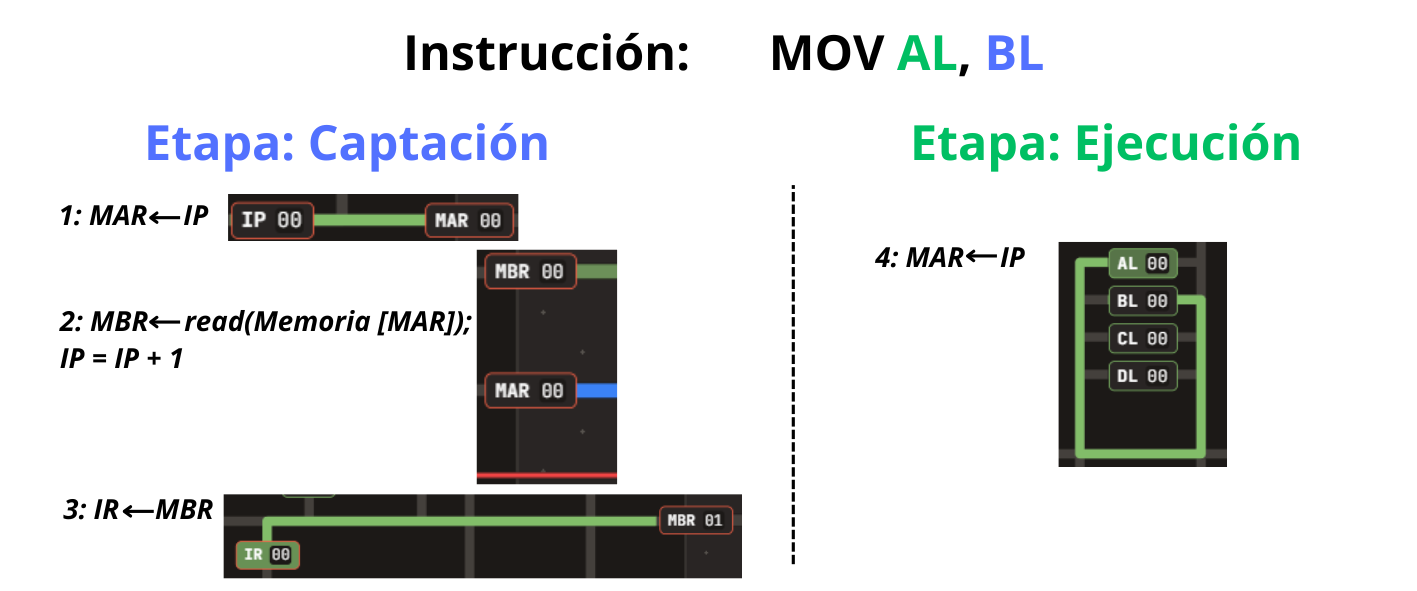

La Figura 5.20 ilustra el flujo básico del ciclo de instrucción implementado en el simulador, permitiendo visualizar los pasos secuenciales de búsqueda, decodificación y ejecución.

Figura 5.20: Flujo del ciclo de instrucción en VonSim8

5.3.1 Etapa de Captación:

En esta etapa, común a todas las instrucciones, consiste en la lectura de la instrucción desde la memoria.

MAR\(\leftarrow\)IP: el contenido del registro puntero de instruccionesIPse transfiere al registro de direcciones de memoriaMAR. La UC genera la señal necesaria para seleccionar el valor delIPy copiarlo en elMAR.MDR\(\leftarrow\)read(Memoria[MAR]);IP\(\leftarrow\)IP+ 1: la UC activa la señal de lectura (read) hacia la memoria, utilizando el valor delMARcomo dirección. El dato leído se transfiere al registro de datos de memoriaMBRa través del bus de datos. Simultáneamente, elIPse incrementa en 1 para apuntar al siguiente byte.IR\(\leftarrow\)MBR: el contenido delMBRse transfiere al registro de instruccionesIR, completando la etapa de captación.

5.3.2 Etapa de Ejecución:

En esta etapa, las operaciones específicas dependen del tipo de instrucción. A continuación, se describen algunos casos representativos:

- MOV

Rx,Ry(Copia entre registros)Rx\(\leftarrow\)Ry: el contenido del registroRyse copia en el registroRx.

- MOV

Rx,[Dirección](Carga a registro)MAR\(\leftarrow\)IP: el valor delIPse transfiere aMAR.MBR\(\leftarrow\)read(Memoria[MAR]);IP\(\leftarrow\)IP+ 1: se lee (read) de memoria el contenido de la dirección indicada porMARy se almacena enMBR.Simultáneamente, elIPse incrementa.MAR\(\leftarrow\)MBR: el contenido deMBRse transfiere aMAR.MBR\(\leftarrow\)read(Memoria[MAR]): se lee de memoria el contenido de la dirección indicada porMARy se almacena enMBR.Rx\(\leftarrow\)MBR: el contenido delMBRse copia al registroRx.

- MOV

[Dirección],Ry(Almacenar en memoria)- igual que MOV

Rx,[Dirección].

- igual que MOV

MBR\(\leftarrow\)Ry: el contenido deRyse transfiere aMBR.write(Memoria[MAR])\(\leftarrow\)MBR: el contenido deMBRse escribe (write) en memoria en la dirección apuntada por elMAR.

- ADD

Rx,[Dirección](Sumar a registro)- igual que MOV

Rx,[Dirección].

- igual que MOV

Rx\(\leftarrow\)Rx+MBR: la Unidad Aritmético-Lógica (ALU) realiza la suma entreRxyMBR, almacenando el resultado enRx. El Registro de EstadoRSse actualiza con los indicadores correspondientes.

- SUB

[Dirección],Ry(Restar a memoria)- igual que MOV

Rx,[Dirección].

- igual que MOV

MBR\(\leftarrow\)Ry-MBR: la ALU resta el contenido deMBRal deRy, almacenando el resultado enMBR. ElRSse actualiza.write(Memoria[MAR])\(\leftarrow\)MBR: el contenido deMBRse escribe en memoria en la dirección apuntada por elMAR.

- CMP

Rx,[Dirección](Comparar a registro)- igual que MOV

Rx,[Dirección].

- igual que MOV

Rx-MBR: la ALU realiza la resta entre el contenido deRxyMBR. Aunque el resultado no se almacena, elRSse actualiza con los indicadores de comparación.

- JMP

Dirección(Salto incondicional)- igual que MOV

Rx,[Dirección].

- igual que MOV

IP\(\leftarrow\)MBR: El contenido delMBRse transfiere al registroIP, estableciendo la nueva dirección de ejecución.

- JC

Dirección(Salto condicional si C=1)- Igual que MOV

Rx,[Dirección].

- Igual que MOV

Si C== 1:IP\(\leftarrow\)MBR: si la bandera de acarreo (C) está activa, el contenido delMBRse transfiere al registroIP.

- JZ

Dirección(Salto condicional si Z=1)- igual que MOV

Rx,[Dirección].

- igual que MOV

Si Z== 1:IP\(\leftarrow\)MBR: si la bandera de cero (Z) está activa, el contenido delMBRse transfiere al registroIP.

5.3.3 Ciclo de la instrucción: modos adicionales

- MOV

Rx,[BL](Carga indirecto)MAR\(\leftarrow\)IP: El valor delIPse transfiere aMAR.MBR\(\leftarrow\)read(Memoria[MAR]);IP\(\leftarrow\)IP+ 1: Se lee (read) de memoria el contenido de la dirección indicada porMARy se almacena enMBR.Simultáneamente, elIPse incrementa.MAR\(\leftarrow\)BL: El contenido deBLse transfiere aMAR.MBR\(\leftarrow\)read(Memoria[MAR]): Se lee de memoria el contenido de la dirección indicada porMARy se almacena enMBR.Rx\(\leftarrow\)MBR: El contenido delMBRse copia al registroRx.

- MOV

Rx,Dato(Carga valor inmediato)MAR\(\leftarrow\)IP: El valor delIPse transfiere aMAR.MBR\(\leftarrow\)read(Memoria[MAR]);IP\(\leftarrow\)IP+ 1: Se lee (read) de memoria el contenido de la dirección indicada porMARy se almacena enMBR.Simultáneamente, elIPse incrementa.Rx\(\leftarrow\)MBR: El contenido delMBRse copia al registroRx.