2.6 Arquitectura x86

Esta sección complementa la caracterización introductoria presentada en la Sección 2.3.1, profundizando en la evolución y los rasgos distintivos de la arquitectura x86. Introducida en 1978 con el Intel 8086 (16 bits), esta familia de procesadores incorporó hitos relevantes como el Intel 80386 (32 bits, 1985) y la extensión AMD64 (64 bits, 2003), con mejoras sostenidas en rendimiento, direccionamiento de memoria y compatibilidad con software legado (Stallings 2021; Intel Corporation 2025, 1979; AMD 2024; Abel 2000; Brey 2013).

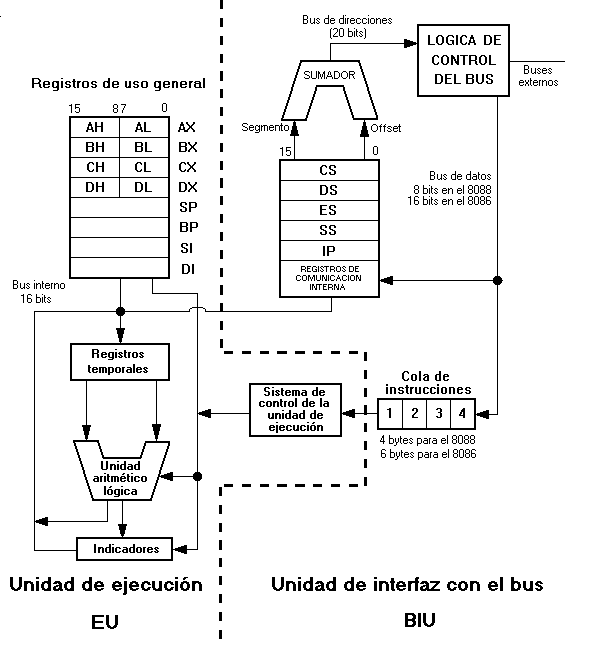

La Figura 2.8 muestra un diagrama esquemático del microprocesador Intel 8086, donde se visualizan los principales bloques funcionales: registros de uso general, unidad de ejecución (EU), unidad de interfaz con el bus (BIU), lógica de control, cola de instrucciones y sistema de control. Esta representación gráfica facilita la comprensión de la organización interna del procesador, destacando la interacción entre los componentes y la estructura modular que caracteriza a la arquitectura x86.

Figura 2.8: Diagrama esquemático microprocesador Intel 8086

2.6.1 Evolución de la arquitectura x86

Uno de los pilares del éxito de la arquitectura x86 ha sido su retrocompatibilidad, permitiendo la ejecución de aplicaciones de 16, 32 y 64 bits en un mismo sistema. Dicha propiedad no solo ha garantizado la continuidad del ecosistema x86, sino que también ha protegido las inversiones en software y sistemas operativos, una característica fundamental en entornos empresariales y académicos.

La Tabla 2.6 sintetiza los principales hitos en la evolución de los procesadores x86, destacando las innovaciones tecnológicas que han marcado su desarrollo a lo largo del tiempo.

| Procesador | Año de Lanzamiento | Número de Bits | Extensiones de 64 bits |

|---|---|---|---|

| Intel 8086 | 1978 | 16 | Arquitectura inicial |

| Intel 80386 | 1985 | 32 | Memoria virtual |

| AMD64 | 2003 | 64 | Extensiones de 64 bits |

La Tabla 2.7 ilustra la progresión histórica de la arquitectura x86, destacando los avances tecnológicos que han impulsado el desarrollo de la informática y ampliado sus fronteras.

| Año | Procesador | Innovación |

|---|---|---|

| 1978 | Intel 8086 | Introducción de la arquitectura x86, 16 bits |

| 1982 | Intel 80286 | Modos de operación adicionales |

| 1985 | Intel 80386 | Arquitectura de 32 bits, memoria virtual |

| 1989 | Intel 80486 | Unidad de punto flotante integrada, mejor caché |

| 1993 | Intel Pentium | Ejecución superescalar, predicción de saltos |

| 1995 | Intel Pentium Pro | Ejecución fuera de orden, caché L2 integrada |

| 2003 | AMD64 | Extensiones a 64 bits, mayor acceso a memoria |

| 2006 | Intel Core | Optimización de rendimiento y eficiencia energética |

2.6.2 Repertorio de instrucciones x86

La arquitectura x86 destaca por su complejidad y flexibilidad, reflejada en un repertorio de instrucciones extenso y de longitud variable. Esto contrasta con arquitecturas RISC, donde predominan instrucciones de longitud fija y decodificación sencilla (John L. Hennessy and Patterson 2017a; Brey 2013). Aunque esta flexibilidad implica una mayor capacidad expresiva y compatibilidad hacia atrás, también introduce desafíos de diseño, tales como la necesidad de decodificadores complejos, técnicas de predicción de instrucciones y ejecución fuera de orden para lograr un rendimiento competitivo.

2.6.2.1 Estructura de una instrucción x86

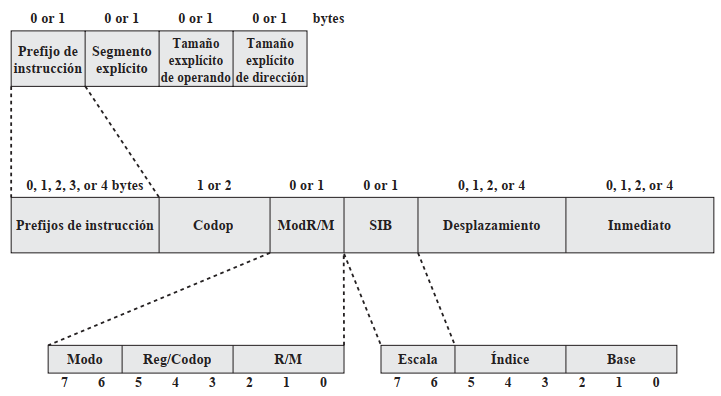

Una instrucción típica en la arquitectura x86 puede estar compuesta por diversos elementos, entre los que se destacan los siguientes (Stallings 2021):

- Prefijos: modifican la operación principal de la instrucción. Por ejemplo, el prefijo

0x66cambia el tamaño del operando. - Código de operación (Opcode): indica la operación a realizar. Por ejemplo,

0x89correspondeMOV. - Modificadores de dirección (ModR/M y SIB): definen registros y direccionamiento. El byte SIB (Scale, Index, Base) es especialmente útil para operaciones complejas, como el acceso a matrices.

- Desplazamiento e inmediato: Agregan flexibilidad en el manejo de datos, aunque aumentan la complejidad.

La Figura 2.9 representa esquemáticamente el formato de las instrucciones en procesadores Pentium x86, destacando la estructura interna y la disposición de los campos principales. Esta visualización facilita la comprensión de cómo se organizan los componentes de una instrucción, permitiendo analizar el impacto de cada elemento en la decodificación, la versatilidad y el rendimiento del procesador.

Figura 2.9: Formato de instrucciones del Pentium x86

Un ejemplo típico de instrucción es:

; Carga en el registro AX el valor almacenado en la dirección de memoria

; que resulta de sumar el contenido de los registros BX y SI más el desplazamiento 16.

MOV AX, [BX+SI+16]Esta instrucción utiliza varios componentes, que el procesador debe decodificar antes de ejecutarla. Aunque esta flexibilidad es una ventaja en términos de funcionalidad, requiere técnicas avanzadas, como predicción de saltos y paralelización, para mantener la eficiencia en procesadores modernos (John L. Hennessy and Patterson 2017a; Patterson et al. 2014; Brey 2013).