5.1 Requisitos de la herramienta

Esta sección expone los requisitos que orientaron el diseño del simulador, clasificados en dos dimensiones complementarias: pedagógica y funcional. La primera se vincula con los objetivos formativos definidos en el capítulo introductorio (1), mientras que la segunda refiere a las características técnicas necesarias para garantizar su implementación eficaz. La definición de los requisitos se apoyó en principios pedagógicos y técnicos, complementados con una validación empírica realizada mediante entrevistas semiestructuradas a docentes expertos (ver Apéndice: Anexo A 6.1). Estas entrevistas revelaron, entre otros aspectos, la necesidad de incorporar visualizaciones gráficas del ciclo de instrucción, soporte para interrupciones y periféricos, y un repertorio reducido de instrucciones con activación progresiva, para evitar la sobrecarga cognitiva en los estudiantes. Asimismo, se identificaron limitaciones en herramientas existentes, como el Emu8086, cuya interfaz y funcionalidades no satisfacen completamente las necesidades pedagógicas. Este proceso permitió identificar necesidades auténticas del aula y carencias específicas en las herramientas existentes, aportando una base empírica rigurosa para la formulación pedagógica y técnica de los requisitos (Huberman et al. 2019).

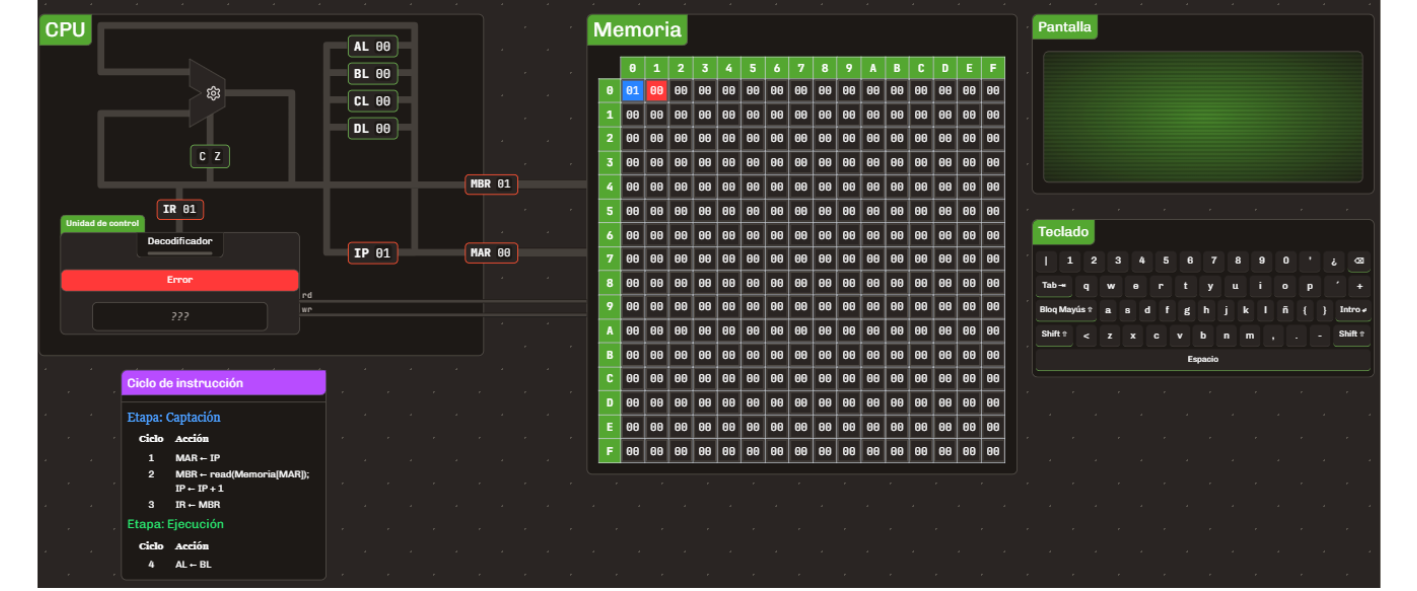

- Visualización de la estructura general de la computadora: La representación gráfica de la CPU, los buses, la memoria y los dispositivos de entrada/salida resulta fundamental para visualizar la interacción y el funcionamiento integrado de los componentes durante el ciclo de instrucción. La Figura 5.1 muestra la estructura general del simulador VonSim8, destacando los elementos activos en cada etapa y facilitando una comprensión sistémica del proceso de ejecución. Este recurso didáctico, respaldado por estudios sobre visualización en disciplinas técnicas (Sorva 2013), contribuye significativamente a la asimilación de conceptos abstractos y al desarrollo de competencias en arquitectura de computadoras.

Figura 5.1: Estructura general del simulador VonSim8

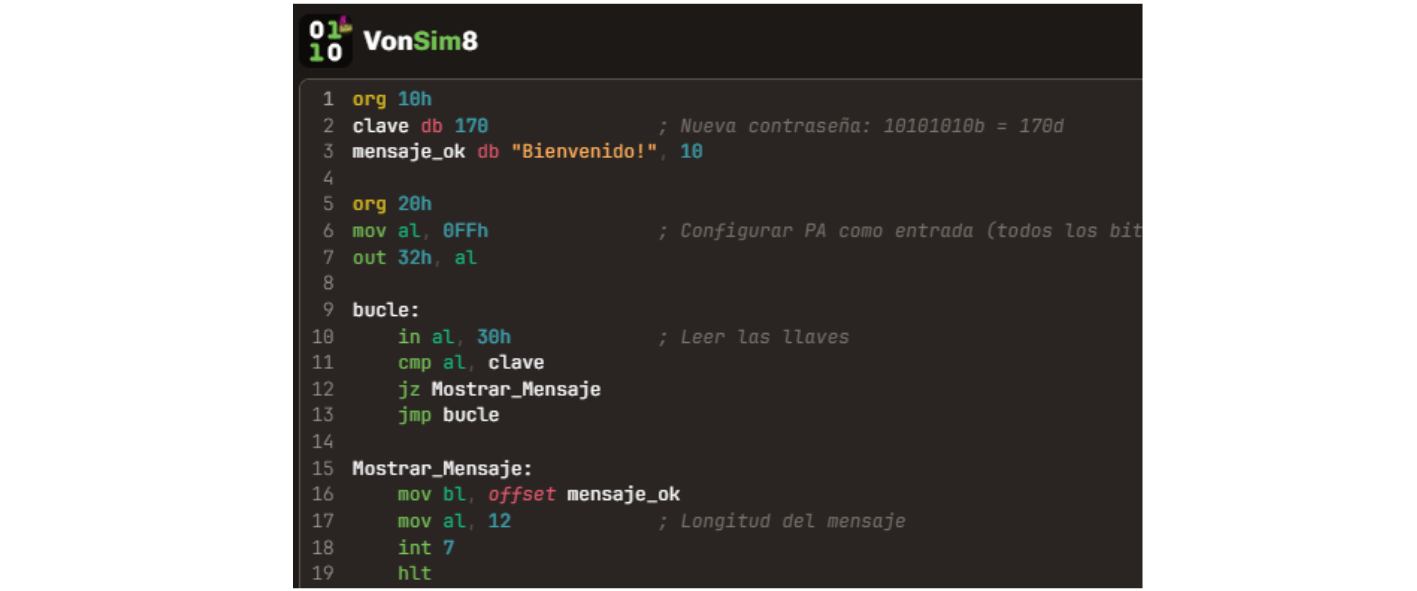

- Soporte para la generación y ejecución de programas en ensamblador: La posibilidad de ejecutar programas escritos en lenguaje ensamblador, tanto de manera paso a paso como en ejecución continua, constituye un recurso esencial para el análisis detallado de cada instrucción. Esta funcionalidad fortalece las competencias en trazado y depuración de código ensamblador, aspectos fundamentales para comprender la interacción entre software y hardware. Para facilitar este proceso, se incorpora un editor de ensamblador dotado de funciones avanzadas, como el resaltado de sintaxis y el autocompletado. Estas características, alineadas con los principios de diseño de interfaces orientados a la usabilidad y accesibilidad (W3C Web Accessibility Initiative 2021), optimizan la experiencia del usuario y favorecen la escritura y comprensión del código. El editor permite al usuario escribir, editar, guardar y ejecutar programas en ensamblador directamente dentro del simulador, además de ofrecer ejemplos predefinidos como apoyo didáctico. La integración de entornos de desarrollo integrados (IDEs) en contextos educativos ha demostrado ser eficaz para la enseñanza de lenguajes de programación, según diversos estudios (McCracken et al. 2001). La Figura 5.2 ilustra la interfaz del editor ensamblador implementado en el simulador, evidenciando las funcionalidades mencionadas y su aporte al proceso de aprendizaje.

Figura 5.2: Editor ensamblador

- Repertorio reducido de instrucciones con activación progresiva: Se selecciona un subconjunto esencial del conjunto de instrucciones x86, el cual se habilita de manera secuencial a lo largo del proceso de enseñanza, en estrecha correspondencia con el avance de los contenidos curriculares. Esta decisión responde a principios de la psicología cognitiva, que sostienen que la introducción gradual de contenidos técnicos favorece la retención y disminuye la sobrecarga cognitiva (National Academies of Sciences, Engineering, and Medicine 2018). Diversos autores, como Hasan (Akram and Sawalha 2019a), Null y Lobur (Null 2023), y Stallings (Stallings 2021), respaldan este enfoque, recomendando la incorporación escalonada de conceptos en la enseñanza de arquitecturas complejas. La activación progresiva del repertorio de instrucciones promueve el desarrollo paulatino de competencias, evitando que los estudiantes se enfrenten prematuramente a la totalidad del conjunto instruccional. Este método se fundamenta en teorías de aprendizaje que destacan los beneficios de la exposición gradual a nuevos conceptos para mejorar la comprensión y la retención (Sweller, Ayres, and Kalyuga 2010). La Tabla 5.1 resume el proceso de activación progresiva del repertorio de instrucciones, especificando las fases de incorporación y los objetivos didácticos correspondientes a cada etapa. Esta representación facilita la comprensión de cómo la introducción gradual de instrucciones contribuye al desarrollo de competencias específicas y potencia el aprendizaje en arquitectura de computadoras.

| Fase | Instrucciones activadas | Objetivo didáctico |

|---|---|---|

| Inicial | MOV, ADD, SUB, HLT | Comprensión del ciclo de instrucción básico |

| Intermedia | CMP, JMP, Jxx | Introducción a control de flujo |

| Avanzada | CALL, RET, INT, IRET, CLI, STI, IN, OUT, POP, PUSH | Manejo de periféricos e interrupciones |

- Simulación visual e interactiva de micropasos de instrucciones:

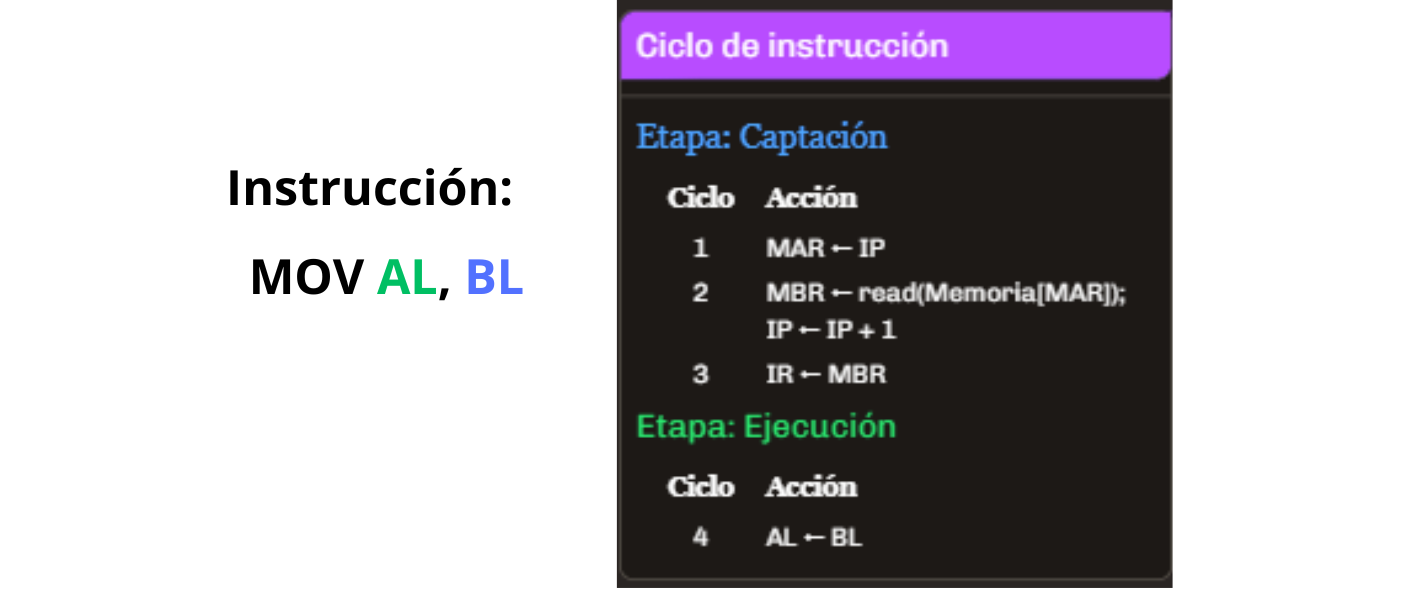

Se implementa una visualización interactiva del flujo de datos basada en el modelo de Nivel de Transferencia entre Registros (Register Transfer Level, RTL). Este enfoque permite representar con precisión el desplazamiento de datos entre registros, buses y unidades funcionales del procesador, así como las señales de control involucradas en cada fase del ciclo de instrucción (Newhall et al. 2025; Harris and Harris 2015). Stallings (Stallings 2021) propone utilizar el modelo RTL para representar el ciclo de instrucción, desde la captura (Fetch) hasta la ejecución (Execute), facilitando la visualización del recorrido de datos y señales de control en cada etapa del proceso. La Figura 5.3 representa de manera visual y secuencial las etapas fundamentales del ciclo de instrucción, ejemplificadas mediante la operación

MOV AL, BL. En la etapa de captación (Fetch), se observa cómo la dirección de la instrucción es transferida del registroIPalMAR, seguida por la lectura de la memoria hacia elMBRy su posterior carga en elIR. En la etapa de ejecución (Execute), el dato se mueve desde el registroBLal registroAL, ilustrando el flujo de información y el funcionamiento interno del procesador durante la ejecución de una instrucción. Esta representación facilita la comprensión didáctica de los procesos involucrados en el ciclo de instrucción.

Figura 5.3: Ciclo de instrucción: captación y ejecución

- Gestión básica de interrupciones y periféricos:

La incorporación de un vector de interrupciones predefinido permite simular eventos externos, como la entrada de datos mediante teclado o la salida de información a través de un monitor. Ante la recepción de una interrupción, el simulador activa la señal

INTR, detiene la ejecución actual y transfiere el control a la rutina correspondiente, facilitando la exploración interactiva de conceptos clave como la asincronía, el manejo de eventos y la interrupción del flujo secuencial. Estos aspectos, característicos de arquitecturas modernas, resultan fundamentales para el entendimiento de sistemas reales y se alinean con las recomendaciones de Null y Lobur (Null 2023), quienes destacan la importancia de abordar estos conceptos en etapas tempranas de la formación. Adicionalmente, se implementa un módulo genérico de entrada/salida programada (Programmed Input/Output, PIO), que actúa como interfaz entre la CPU y los dispositivos periféricos. Este módulo posibilita la simulación de operaciones mediante instrucciones como IN y OUT, permitiendo al estudiante interactuar con dispositivos representados gráficamente, como interruptores y teclas. De esta manera, se favorece una comprensión más tangible de los mecanismos subyacentes al intercambio de información entre el procesador y los dispositivos externos. La Figura 5.4 muestra el módulo PIO y su interacción con los periféricos, ilustrando visualmente la estructura y funcionamiento de este componente dentro del simulador.

Figura 5.4: Módulo genérico de entrada/salida programada (PIO)

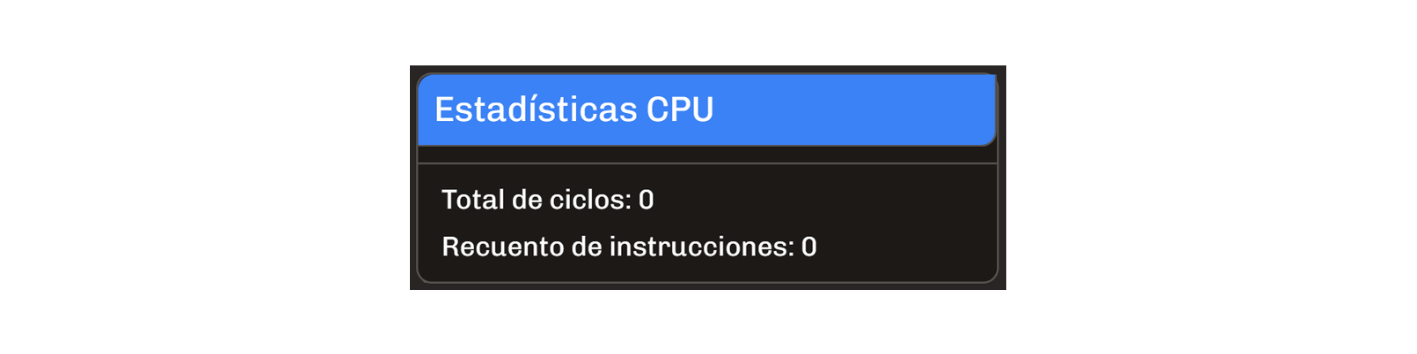

- Métricas de rendimiento: La integración de indicadores clave, como el tiempo de ciclo, el tiempo de CPU y los ciclos por instrucción (Cycles Per Instruction, CPI), generados automáticamente a partir de la ejecución de los programas, permite al estudiante analizar cuantitativamente la eficiencia del sistema. Además, la posibilidad de configurar la frecuencia del CPU en un rango de valores (1–10 Hz) facilita la comparación entre diferentes implementaciones y escenarios de ejecución. La disponibilidad de estas métricas contribuye a fortalecer la comprensión de aspectos fundamentales del rendimiento del procesador, promoviendo una formación integral que abarca tanto dimensiones funcionales como métricas del comportamiento del sistema (John L. Hennessy and Patterson 2017a). La Figura 5.5 presenta el panel de métricas de rendimiento implementado en el simulador, donde se visualizan los principales indicadores y configuraciones disponibles para el análisis cuantitativo.

Figura 5.5: Métricas de rendimiento

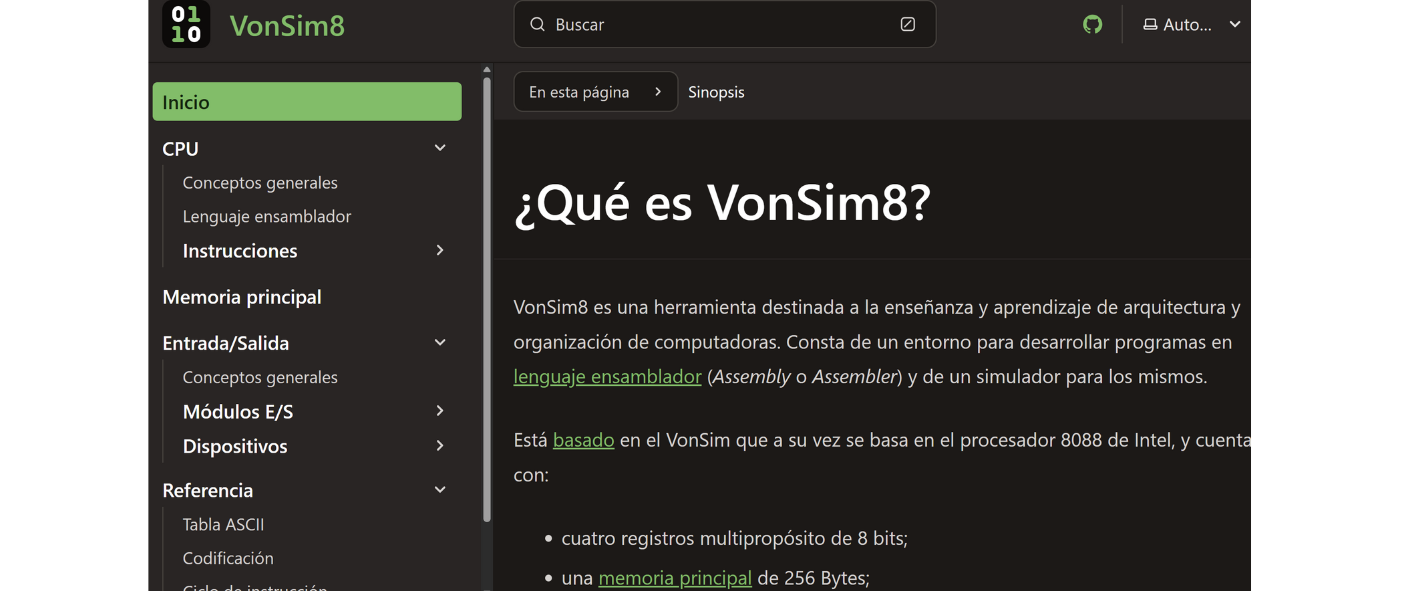

- Documentación y recursos de apoyo: La disponibilidad de documentación clara y accesible resulta esencial para explicar el funcionamiento del simulador, sus componentes y las instrucciones disponibles. Este recurso debe incluir ejemplos prácticos, guías de uso y materiales complementarios que faciliten la comprensión y el aprendizaje autónomo. La incorporación de tutoriales interactivos y ejemplos prácticos es fundamental para orientar al estudiante en el uso efectivo del simulador, promoviendo un aprendizaje activo y reflexivo (Bonwell and Eison 1991). La Figura 5.6 muestra la interfaz de la documentación en línea, donde se presentan los contenidos organizados y los recursos de apoyo disponibles para el usuario.

Figura 5.6: Documentación on line

La Tabla 5.2 sintetiza los requisitos funcionales que sustentan el diseño del simulador, junto con su fundamentación pedagógica y técnica. Este resumen permite valorar cómo cada requisito aporta a la pertinencia educativa y a la viabilidad tecnológica de la herramienta, integrando criterios de diseño orientados a optimizar el proceso de enseñanza y aprendizaje en arquitectura x86 mediante recursos visuales, interactivos y métricos.

| Requisito | Fundamento pedagógico / técnico |

|---|---|

| Visualización de estructura general | Facilita comprensión sistémica mediante representaciones gráficas de hardware. |

| Soporte para programas en ensamblador | Desarrolla competencias en trazado y depuración de lenguaje ensamblador; mejora usabilidad. |

| Repertorio reducido y activación progresiva | Disminuye sobrecarga cognitiva al introducir instrucciones de manera escalonada. |

| Simulación visual de micropasos (RTL) | Permite comprender el flujo interno de datos y señales de control durante el ciclo de instrucción. |

| Gestión de interrupciones y periféricos | Simula asincronía y manejo de eventos, favoreciendo la comprensión de sistemas reales. |

| Métricas de rendimiento | Promueve análisis cuantitativo de eficiencia (CPI, ciclos, tiempo de CPU). |

| Documentación y recursos de apoyo | Fomenta aprendizaje autónomo y activo mediante guías, tutoriales y ejemplos. |

La definición de los requisitos funcionales y pedagógicos permitió identificar la necesidad de simplificar la arquitectura x86 para adaptarla a los objetivos educativos. Esta simplificación asegura que los estudiantes puedan concentrarse en los conceptos fundamentales sin verse abrumados por la complejidad técnica. A continuación, se detalla la justificación de esta decisión.