5.5 Adaptaciones y mejoras en VonSim8

Si bien VonSim ofrece una base sólida para la enseñanza de arquitectura de computadoras, su complejidad funcional puede resultar abrumadora para estudiantes en etapas iniciales. Por esta razón, se implementaron modificaciones estratégicas en VonSim8, orientadas a simplificar el modelo y alinearlo con los objetivos pedagógicos de la asignatura. A continuación, se describen las principales mejoras realizadas.

Las modificaciones implementadas se alinean con los contenidos curriculares de la asignatura y están fundamentadas en los principios del aprendizaje activo (Bonwell and Eison 1991).

- Simplificación del repertorio instruccional para una introducción gradual;

- Reducción a registros y memoria de 8 bits, coherente con la escala de enseñanza;

- Interfaz gráfica esquemática que muestra el flujo de ejecución;

- Funciones interactivas para observar explícitamente el ciclo de instrucción y la interacción de componentes;

- Ocultamiento inicial de las banderas O (overflow) y S (signo), y visualización dinámica de la bandera I (interrupciones);

- Menú de controles modificado y adaptado al uso pedagógico;

- Registros con entrada y salida independientes; ocultamiento automático de SP, ri e id;

- Eliminación de los registros temporales left, right y result en la ALU;

- Resaltado dinámico en memoria de las posiciones apuntadas por IP y SP;

- Vector de interrupciones de 8 posiciones (0x00h–0x07h) y mapeo directo INT→dirección;

- Visor de instrucciones y datos del programa, con tamaño en bytes y etiquetas;

- Compatibilidad con directivas ORG y END (por defecto 0x00h o 0x08h; compatibilidad con org 0x20h);

- Decodificador con memoria de control y secuenciador para microoperaciones y señales de control;

- Tour de aprendizaje, centro de ayuda y ejemplos integrados.

A continuación se detallan los cambios más relevantes implementados en VonSim8, junto con capturas de pantalla que ilustran las modificaciones realizadas:

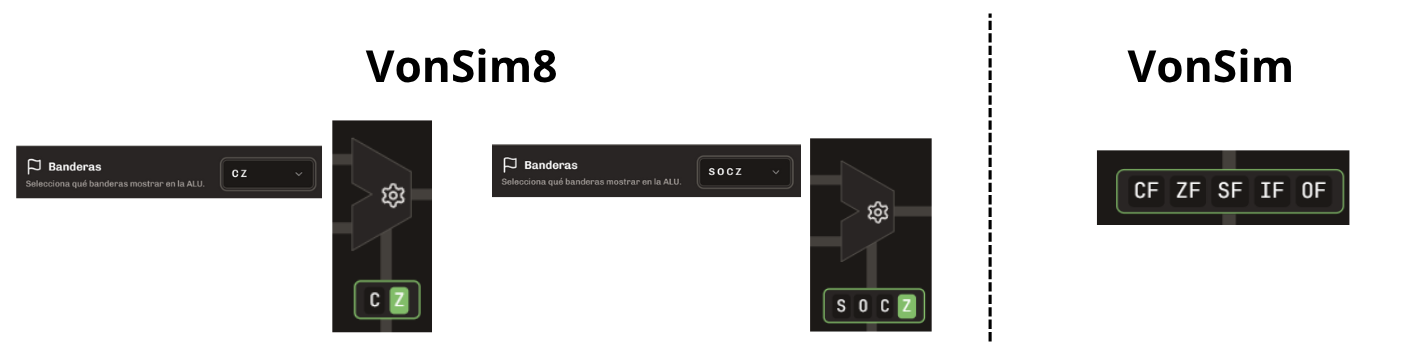

En el registro Flags del simulador VonSim8, las banderas O (overflow) y S (signo) se mantienen ocultas durante los primeros ejercicios de ensamblador, dado que inicialmente solo se emplean números enteros positivos. Esta decisión pedagógica simplifica la interfaz y reduce la carga cognitiva en las etapas iniciales del aprendizaje. Sin embargo, dichas banderas pueden habilitarse posteriormente desde el menú de configuración del simulador, a medida que se abordan ejercicios de mayor complejidad que requieren el análisis de operaciones con signo y detección de desbordamientos.

La Figura 5.9 muestra la representación visual del registro Flags, evidenciando la disposición de las banderas y su configuración dinámica según el nivel de avance del estudiante.

Figura 5.9: Registro Flags

El flag de interrupción I se visualiza únicamente cuando el programa lo requiere, como ocurre al ejecutar instrucciones específicas de interrupción, tales como INT o IRET. Esta funcionalidad permite que los estudiantes observen de manera directa la activación y desactivación del flag, comprendiendo su impacto en el flujo de ejecución y en la gestión de eventos asincrónicos dentro del simulador

La Figura 5.10 muestra la representación gráfica del registro de estado I, evidenciando su comportamiento dinámico y su relevancia en el manejo de interrupciones.

Figura 5.10: Registro de estado I

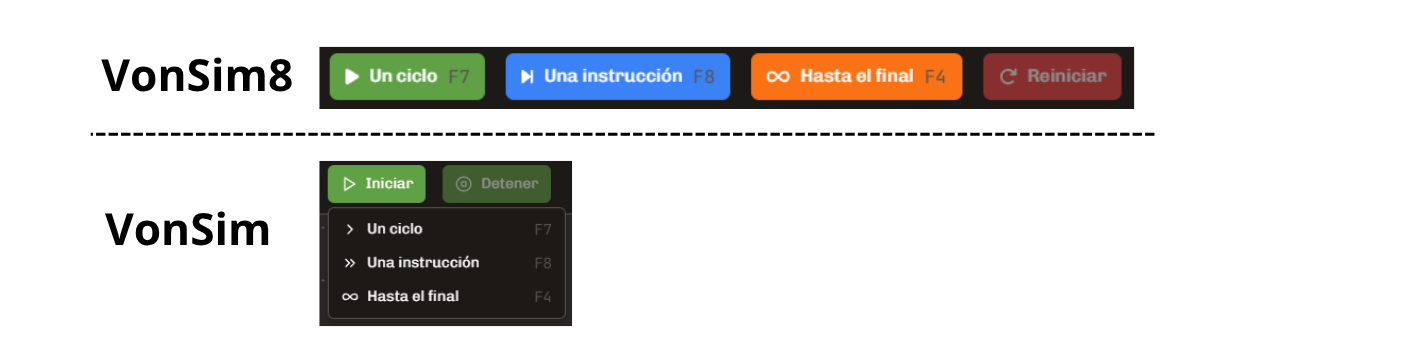

El menú de controles del simulador fue actualizado para optimizar la interacción del usuario y facilitar la ejecución de programas en diferentes modos, como ciclo, instrucción o ejecución completa. Esta mejora contribuye a una experiencia más intuitiva y eficiente, permitiendo al estudiante seleccionar el nivel de granularidad en la simulación y observar el comportamiento del sistema en cada etapa del proceso.

La Figura 5.11 presenta la nueva disposición del menú de controles, destacando las opciones disponibles y su relevancia para el aprendizaje práctico en arquitectura de computadoras.

Figura 5.11: Controles del simulador

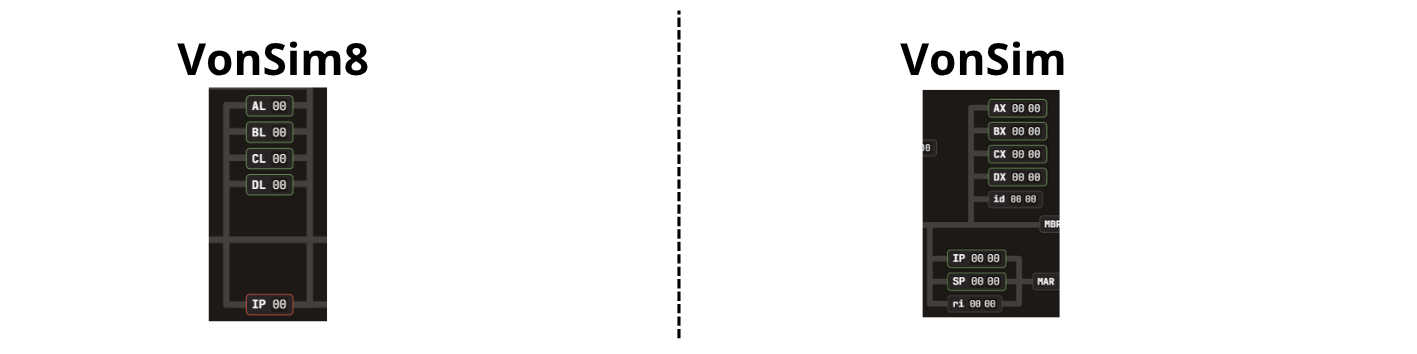

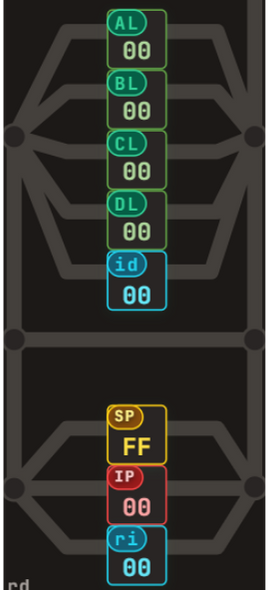

En el simulador se decidió utilizar solo la parte baja de cada registro, en lugar de registros de 16 bits completos. Esta simplificación pedagógica facilita la representación y manipulación de datos, permitiendo una mejor comprensión de los conceptos clave de la arquitectura de computadoras. Además, el diseño unificado de los registros, con entrada y salida independientes, favorece la visualización clara del flujo de datos entre los registros y la ALU, aspecto fundamental para entender el ciclo de instrucción y la interacción de los componentes.

La Figura 5.12 muestra la disposición y estructura de los registros de 8 bits implementados en el simulador, evidenciando su funcionalidad y su aporte a la didáctica del modelo.

Figura 5.12: Registro de 8 bits

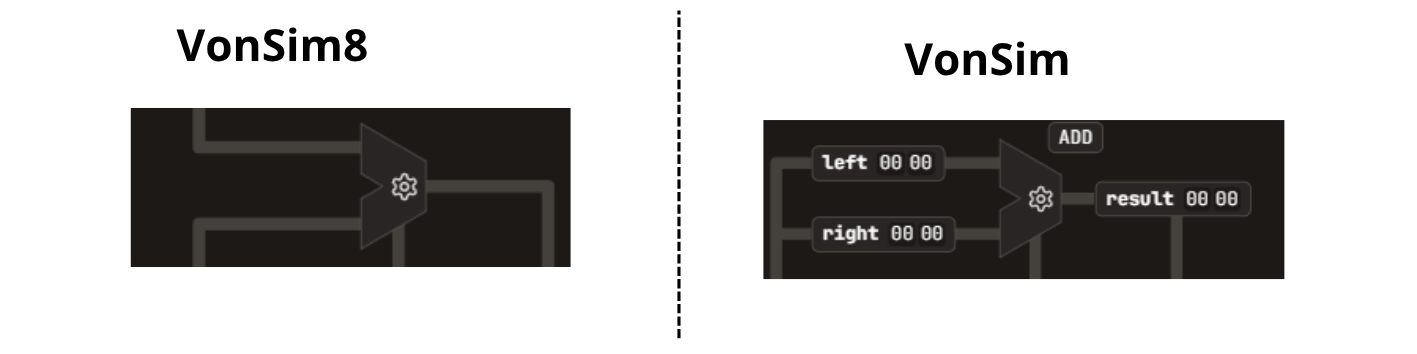

La supresión de los registros temporales left, right y result en la ALU responde al objetivo de simplificar el flujo de datos y disminuir la carga cognitiva de los estudiantes. En lugar de emplear registros intermedios, el simulador representa de manera directa las operaciones realizadas sobre los operandos, lo que facilita la comprensión del funcionamiento aritmético y lógico de la unidad. Esta estrategia didáctica permite al usuario observar de forma más transparente el procesamiento interno, favoreciendo el aprendizaje de los mecanismos fundamentales de la ALU.

La Figura 5.13 ilustra la eliminación de estos registros temporales, mostrando la simplificación lograda en la visualización y el flujo de datos dentro del simulador.

Figura 5.13: Eliminación registro temporales left, right y result

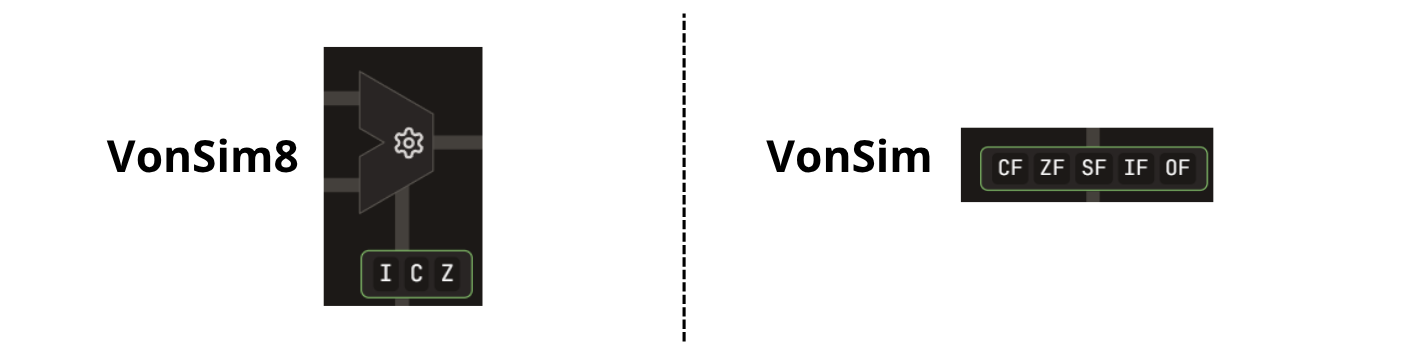

Por motivos pedagógicos, los registros SP, ri e id permanecen ocultos en la interfaz del simulador y solo se habilitan de manera automática cuando una instrucción específica requiere su utilización. Esta estrategia contribuye a simplificar la visualización y a reducir la carga cognitiva durante las etapas iniciales del aprendizaje, permitiendo que el estudiante se enfoque en los componentes esenciales del ciclo de instrucción. La Figura 5.14 muestra la representación gráfica de estos registros, evidenciando su activación dinámica y su función de apoyo en la ejecución de instrucciones.

Figura 5.14: Registro SP, id y ri

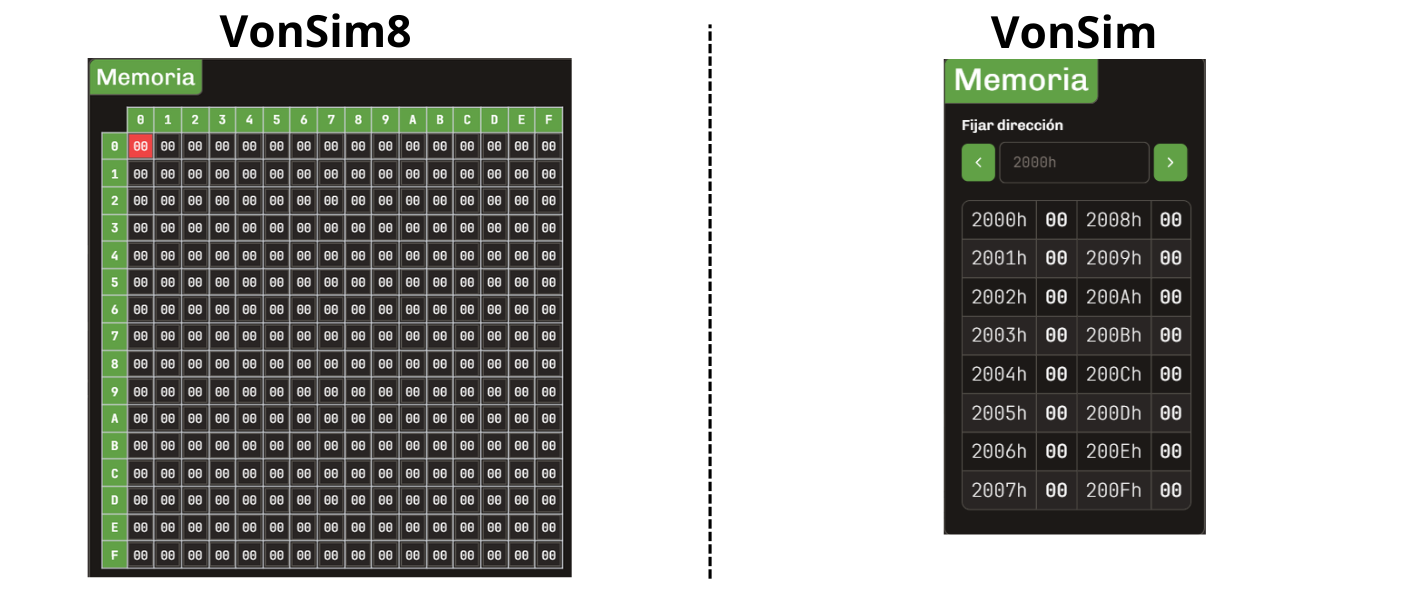

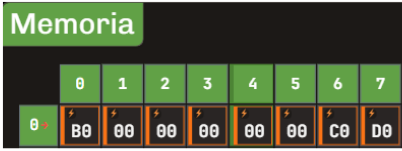

La memoria principal del simulador se representa mediante una matriz de 16×16 celdas en formato hexadecimal, lo que posibilita el almacenamiento de hasta 256 bytes de datos. Este diseño visual facilita la identificación de cada posición de memoria y promueve una comprensión intuitiva de la organización y gestión de datos en la arquitectura implementada. La Figura 5.15 ilustra la estructura matricial de la memoria, destacando su accesibilidad y utilidad para el análisis y la manipulación durante la simulación.

Figura 5.15: Memoria principal

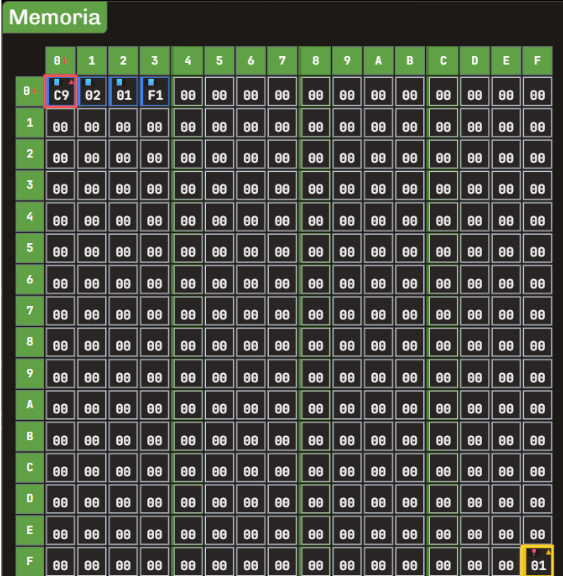

El simulador incorpora un mecanismo visual que destaca, dentro de la memoria principal, las posiciones apuntadas por los registros IP y SP. Esta funcionalidad permite al estudiante identificar de manera inmediata tanto la dirección de la próxima instrucción a ejecutar como la ubicación actual de la cima de la pila, facilitando el seguimiento del flujo de ejecución y la gestión de la memoria durante el ciclo de instrucción. La Figura 5.16 muestra el resaltado simultáneo de estas direcciones, evidenciando su importancia para la comprensión de la dinámica interna del procesador.

Figura 5.16: Resaltado registro IP y registro SP

El simulador VonSim8 destaca visualmente, mediante el uso de color naranja, el espacio reservado en la memoria principal para el vector de interrupciones, que abarca las ocho posiciones comprendidas entre las direcciones 0x00h a 0x07h. Esta representación facilita la identificación del área destinada al manejo de interrupciones, permitiendo al estudiante comprender su ubicación y relevancia dentro de la arquitectura. La Figura 5.17 muestra el resaltado específico de este segmento, evidenciando su función en la gestión de eventos externos y en la organización interna del sistema.

Figura 5.17: Resaltado vector de interrupciones

Para determinar la dirección de la rutina de tratamiento de interrupción en VonSim, es necesario multiplicar el número de interrupción por 4, ya que cada dirección de rutina ocupa 4 bytes. En cambio, en VonSim8 no es necesario realizar esta multiplicación, dado que cada dirección de rutina de interrupción corresponde a un solo byte. Por lo tanto, la interrupción INT 0 se encuentra en la direccion 0x00h, la interrupción INT 6 en la direccion 0x06h, y así sucesivamente.

Con el objetivo de facilitar el análisis y la comprensión del funcionamiento interno del simulador, se incorporó un visor de instrucciones y datos del programa en memoria. Esta herramienta permite al estudiante visualizar, para cada celda de memoria, la instrucción almacenada, el tamaño en bytes que ocupa y la etiqueta asociada a los datos. De este modo, se promueve una interpretación detallada del contenido de la memoria y se favorece el seguimiento del flujo de ejecución durante la simulación. La Figura 5.18 muestra la interfaz del visor, evidenciando su utilidad para el estudio y la manipulación de instrucciones y datos en el entorno educativo.

Figura 5.18: Visor de instrucciones y datos del programa en memoria

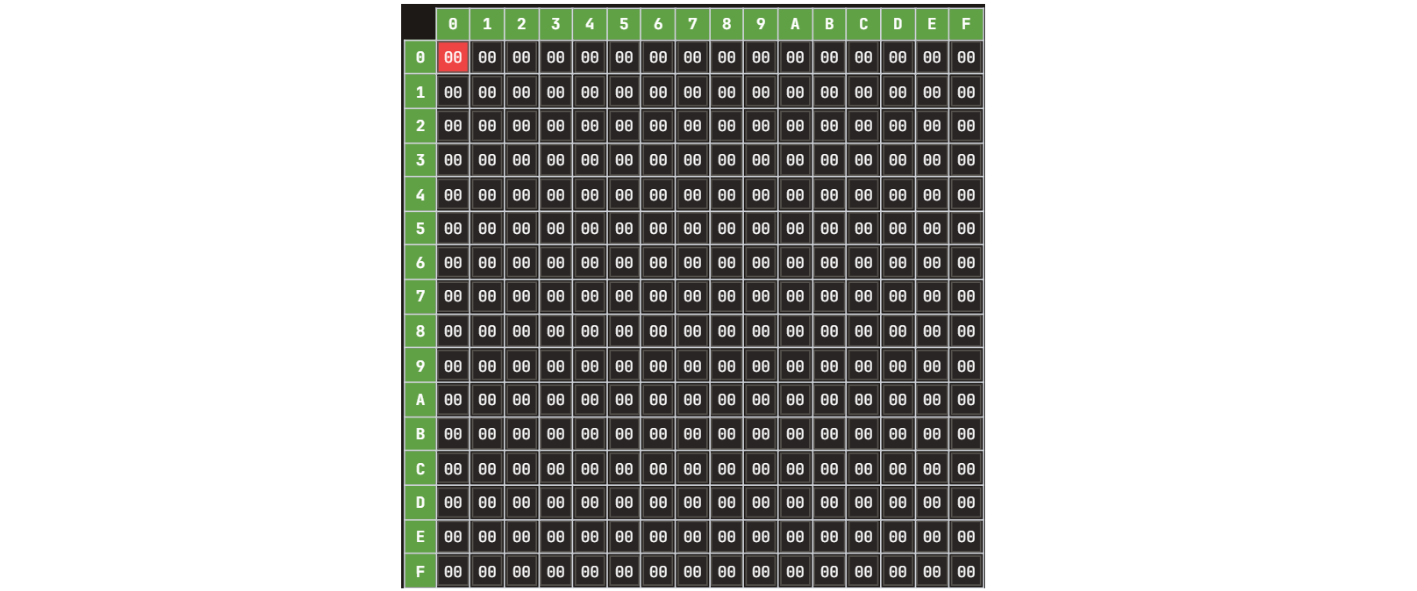

En VonSim, cuando se escribe un programa en el editor del simulador, es obligatorio que la sección de código inicie con la directiva ORG 0x2000h y que termine con la directiva END. Esto se debe a que el simulador comienza a ejecutar la primera instrucción a partir de la dirección de memoria 0x2000h. De manera complementaria, los datos del programa suelen cargarse a partir de la dirección 0x1000h mediante la directiva ORG 0x1000h.

En VonSim8, el uso de la directiva ORG para definir la dirección inicial es opcional. Por defecto, si el programa no incluye esta directiva, la primera instrucción se carga en la dirección 0x00h. En caso de contener instrucciones de interrupción (INT), el simulador asigna automáticamente la dirección 0x08h como punto de inicio, reservando espacio para el vector de interrupciones.

Con el fin de asegurar la compatibilidad con programas desarrollados para VonSim, el simulador VonSim8 permite cargar programas utilizando la directiva ORG, aunque adapta la dirección inicial de ejecución. En lugar de emplear la dirección0x2000h, característica de VonSim, se utiliza la dirección 0x20h en VonSim8, lo que facilita la ejecución de programas en el entorno simplificado. Esta flexibilidad permite a los usuarios definir direcciones personalizadas y mantener la interoperabilidad entre ambos simuladores. La Figura 5.19 muestra ejemplos de programas con la directiva ORG y END, evidenciando la compatibilidad y la adaptación de las direcciones de inicio en cada caso.

Figura 5.19: Compatibilidad directiva ORG y END

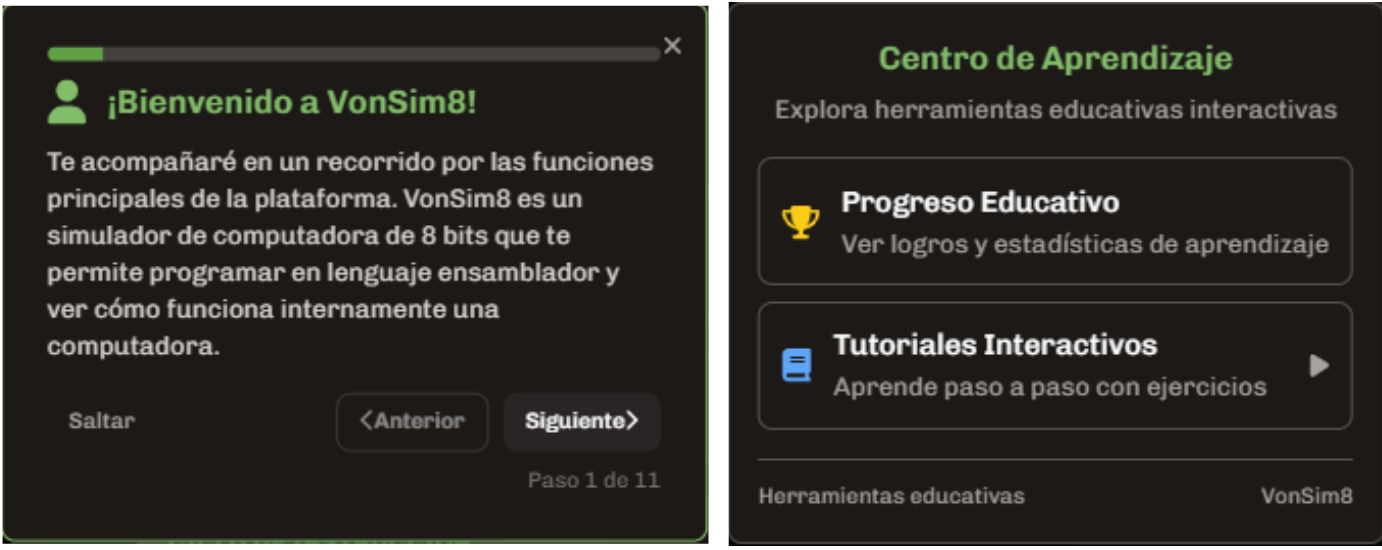

Con el propósito de potenciar la experiencia de aprendizaje, VonSim8 incorpora la posibilidad de abrir ejemplos prácticos directamente desde el simulador, permitiendo al estudiante experimentar con distintos programas y observar su ejecución paso a paso. Además, se ha implementado un tour de aprendizaje interactivo y un centro de ayuda con explicaciones y ejemplos básicos, que facilitan la familiarización con las principales funcionalidades de la herramienta. El editor, dotado de opciones para ampliar el tamaño de fuente y acceder a ejemplos predefinidos, contribuye a una mayor accesibilidad y personalización del entorno de trabajo. La Figura 5.20 muestra la interfaz mejorada del editor, evidenciando su aporte a la didáctica y la autonomía del usuario.

Figura 5.20: Editor con ampliación de fuente y ejemplos

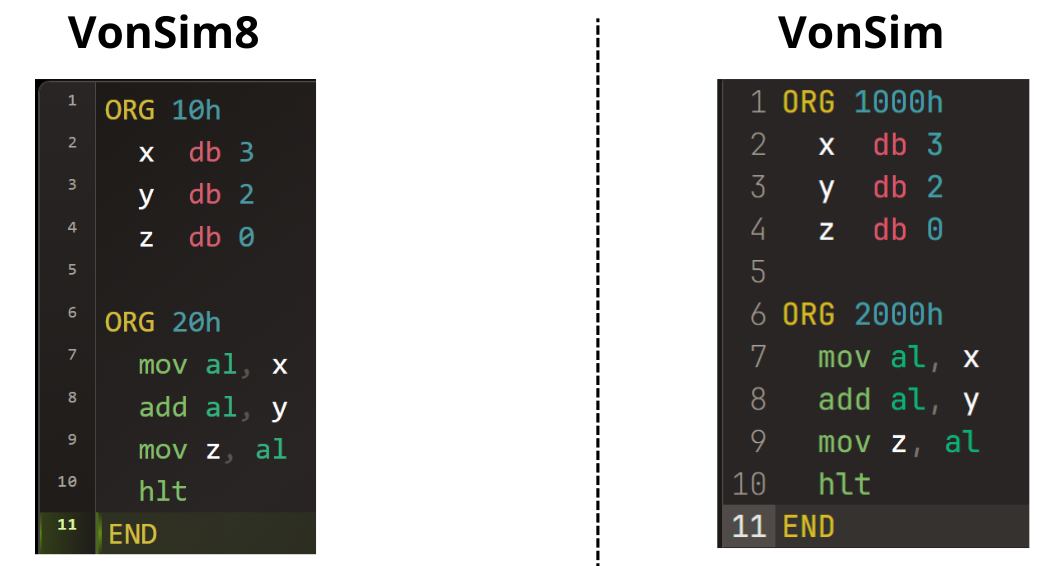

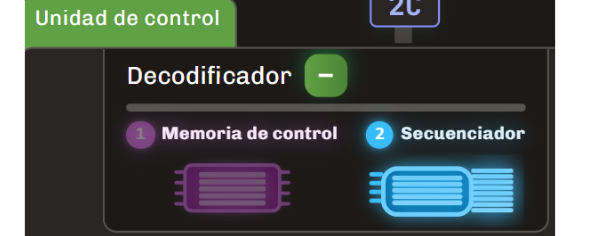

El diseño de la unidad de control en VonSim8 ha sido optimizado mediante la incorporación, dentro del decodificador, de una memoria de control y un secuenciador. Estos elementos permiten representar de manera precisa y detallada el ciclo de instrucción, mostrando las microoperaciones y las señales de control generadas en cada etapa. Esta mejora facilita la comprensión de la coordinación interna del procesador y el funcionamiento de la unidad de control. La Figura 5.21 ilustra la estructura del decodificador, destacando la integración de la memoria de control y el secuenciador como componentes clave para el modelado didáctico de la arquitectura.

Figura 5.21: Decodificador en VonSim8

VonSim8 incorpora un tour guiado e interactivo que introduce didácticamente el entorno de trabajo. Este recorrido orienta al usuario en la identificación de los componentes principales —panel de registros, memoria, repertorio de instrucciones y consola de ejecución—, explicando su función y su articulación dentro del ciclo de ejecución de un programa. De este modo, el estudiante se familiariza progresivamente con la interfaz y con la representación estructural y funcional de los procesos internos del sistema.

Para fortalecer el aprendizaje autónomo y progresivo, VonSim8 incorpora una guía de ejercicios y ejemplos de código ensamblador que permiten al estudiante poner en marcha el simulador y observar, paso a paso, los efectos sobre registros y memoria. Este enfoque exploratorio, basado en la experimentación y la integración de teoría y práctica, se complementa con un tour interactivo y un centro de aprendizaje que ofrecen explicaciones visuales y retroalimentación inmediata. Ambos recursos contribuyen a reducir la curva de aprendizaje y promueven la autonomía del usuario, alineándose con principios constructivistas que privilegian la interacción activa con el entorno. La Figura 5.22 muestra la interfaz del tour de aprendizaje, evidenciando su aporte a la comprensión conceptual y a la familiarización con la arquitectura y el funcionamiento interno del simulador.

Figura 5.22: Tour de aprendizaje en VonSim8

Por motivos de claridad y síntesis, la Tabla 5.6 resume las diferencias más significativas entre VonSim y VonSim8, destacando las modificaciones implementadas en el diseño y su repercusión en la enseñanza de los conceptos esenciales de arquitectura de computadoras. Esta presentación comparativa facilita la identificación de los aspectos pedagógicos y técnicos que distinguen a cada simulador, permitiendo apreciar el impacto de las mejoras realizadas en el proceso formativo.

| Característica | VonSim | VonSim8 |

|---|---|---|

| Registros | Registros de 16 bits (AX, BX, CX, DX) | Registros de 8 bits, con entrada y salida independientes. Registros SP, RI e ID se ocultan y habilitan automáticamente. |

| Registro FLAGS | Incluye todas las banderas del 8088 (O, S, Z, C, etc.) | Se ocultan inicialmente las banderas O (overflow) y S (signo). El flag I (interrupción) se muestra dinámicamente. |

| Controles del simulador | Menú de controles estándar | Menú de controles modificado y adaptado. |

| Directiva org |

Obligatoria. El código comienza en 0x2000h y los datos en 0x1000h.

|

Opcional. Por defecto, el código inicia en 0x00h. Si hay interrupciones, comienza en 0x08h. Compatible con org 0x20h.

|

| Memoria principal | 32 KB, organizada en páginas del 8088. | Matriz de 16×16 bytes (256 bytes), expresada en hexadecimal, con resaltado dinámico de IP y SP. |

| Resaltado de IP y SP | No resalta dinámicamente IP y SP en memoria. | Resalta en memoria la posición apuntada por IP y SP. |

| Vector de interrupciones | Vector de interrupciones ocupa varias posiciones, cada rutina ocupa 4 bytes. |

Vector de interrupciones ocupa 8 posiciones (0x00h a 0x07h), cada rutina ocupa 1 byte.

|

| Dirección de rutina de interrupción | Se multiplica el número de interrupción por 4 para obtener la dirección. |

La dirección de la rutina de interrupción coincide con el número de interrupción (ej. INT 6 en 0x06).

|

| Visor de instrucciones y datos | No incluye visor detallado de instrucciones y datos. | Incluye visor de instrucciones y datos, mostrando tamaño y etiquetas. |

| Temporales de la ALU |

Registros temporales left, right y result visibles.

|

Eliminados, para simplificar la representación del ciclo de instrucción. |

| Unidad de control | Decodificador básico sin memoria de control ni secuenciador. | Decodificador mejorado con memoria de control y secuenciador, permite visualizar microoperaciones y señales de control. |

| Enfoque pedagógico | Mayor fidelidad al procesador Intel 8088, con repertorio más amplio. | Simplificación estratégica para reducir carga cognitiva y favorecer aprendizaje progresivo. |

| Editor y recursos didácticos | Editor estándar, sin ampliación de fuente ni tour de aprendizaje. | Editor con ampliación de fuente, ejemplos prácticos, tour de aprendizaje y centro de ayuda. |